End-to-End sign-off for floating point hardware

Full IEEE 754 compliance, multiple number formats supported for AI/ML accelerator verification.

Floatrix

Floatrix is a vendor-neutral tool that enables exhaustive end-to-end verification for floating-point hardware. Using the powerful language of SystemVerilog Assertions (SVA), our checkers have been optimised for performance to enable end-to-end sign-off using compositional formal methods techniques, guaranteeing a much higher proof convergence on micro-architectural implementations than would be possible with alternative techniques.

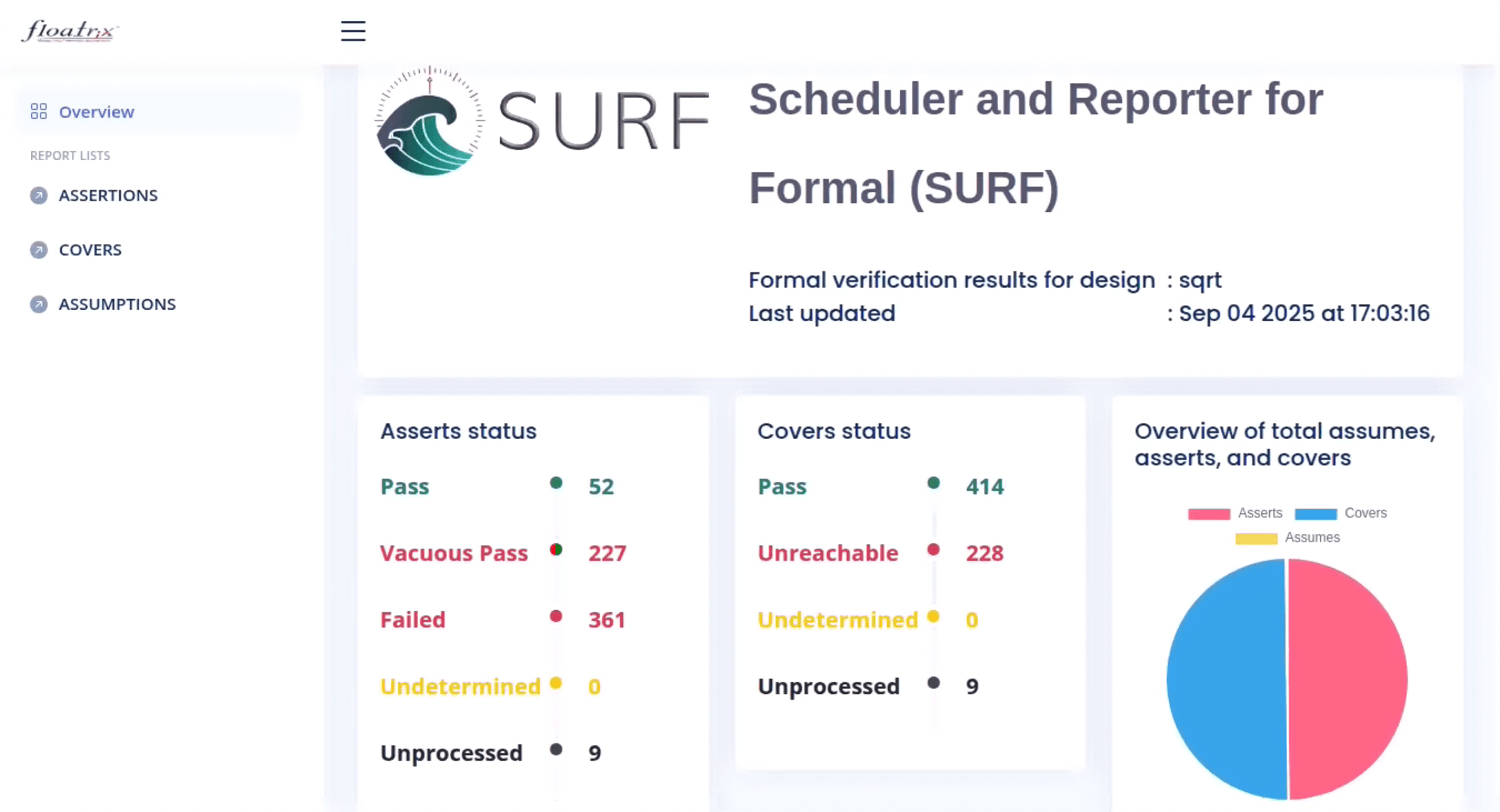

With automation, intelligent debug and supported by six-dimensional coverage and reporting via SURF, we have brought what was missing for end-to-end sign-off of floating-point designs implemented as FP4, FP8, bfloat16, and compliance with IEE754 standard (16, 32 and 64-bit precisions).

Automation

GUI-Based; Report Dashboard.

Debug & Bug Hunting

IEEE 754 support for most operations; smart regression flow; intelligent debugger.

Customisation Options

Various rounding modes available; out-of the box support for half, single, and double precisions; easily configurable and customisable.

Vendor Neutral

Supported on all commercial EDA tools exploiting the solver infrastructure that has been used for years in FPV.